Описание и параметры

Микросхема 32-разрядного высокопроизводительного процессора цифровой обработки сигналов с ОЗУ 12 Мбит и тактовой частотой 230 МГц.

В процессоре можно выделить следующие элементы:

• Четыре блока UART,

• Два блока CANFD (CAN0, CAN1). Интерфейс – КМОП с необходимостью установки внешних микросхем приемопередатчиков CAN PHY,

• Блок Ethernet 10/100/1000 с интерфейсами RMII или RGMII к внешним микросхемам PHY,

• Блок USB с интерфейсом ULPI к внешней микросхеме PHY.

Настройки:

• Управление силой драйверов КМОП,

• В регистр boundary scan добавлены выводы LVDS,

• UART. Добавлена дробная часть делителя частоты bitrate и добавление механизма подсинхронизации,

• I2C. Добавление регистра задания времени удержания для соответствия спецификации,

• Добавлен механизм выбора очередности следования бит при работе с АЦП (для совместимости с АЦП 5101НВ045),

• Исправлены ошибки подключения бит [20:18] порта PC. Их драйвер был всегда включен.

Процессор совместим со средой разработки Visual DSP (для ADSP-TSххх), CM-LYNX.

- два вычислительных модуля: X и Y, каждый из которых содержит умножитель, ALU, CLU, сдвиговое устройство и регистровый файл объемом в 32 слова;

- два блока целочисленных ALU: J и К, каждый из которых содержит 32-битное целочисленное ALU, а также регистровый файл объемом в 32 слова;

- устройство управления (Sequencer), управляющее ходом исполнения программы и содержащее буфер выравнивания команд (instruction alignment buffer – IAB) и буфер целевых адресов перехода (branch target buffer – ВТВ);

- три 128-битные шины, обеспечивающие возможность высокоскоростного обмена между внутренней памятью и другими компонентами ядра процессора (вычислительными блоками, блоками целочисленных ALU, устройством управления и SOC-интерфейсом);

- 128-битная шина, обеспечивающая возможность высокоскоростного обмена между внутренней памятью и периферийными устройствами внешнего ввода/вывода (DMA, внешним портом и LINK-портами);

- SOC-интерфейс, обеспечивающий связь между внутренними шинами ядра и шиной периферийных устройств;

- периферийные устройства: интерфейс внешнего порта, контроллер SDRAM, конвейерный интерфейс со статической организацией конвейера, двенадцать каналов DMA, два порта LVDS-линков (с двумя каналами DMA каждый) и др.;

- 12 Мбит внутренней памяти, организованной как шесть блоков по 2 Мбит, каждый из которых содержит 64 К 32-битных слов;

- средства поддержки отладки;

- тестовый порт JTAG.

• Четыре блока UART,

• Два блока CANFD (CAN0, CAN1). Интерфейс – КМОП с необходимостью установки внешних микросхем приемопередатчиков CAN PHY,

• Блок Ethernet 10/100/1000 с интерфейсами RMII или RGMII к внешним микросхемам PHY,

• Блок USB с интерфейсом ULPI к внешней микросхеме PHY.

Настройки:

• Управление силой драйверов КМОП,

• В регистр boundary scan добавлены выводы LVDS,

• UART. Добавлена дробная часть делителя частоты bitrate и добавление механизма подсинхронизации,

• I2C. Добавление регистра задания времени удержания для соответствия спецификации,

• Добавлен механизм выбора очередности следования бит при работе с АЦП (для совместимости с АЦП 5101НВ045),

• Исправлены ошибки подключения бит [20:18] порта PC. Их драйвер был всегда включен.

Процессор совместим со средой разработки Visual DSP (для ADSP-TSххх), CM-LYNX.

Состояние разработки

ОКР завершена

Варианты поставки изделия

Серийная поставка

Ближайший аналог

ADSP-TS202, ADSP-TS201

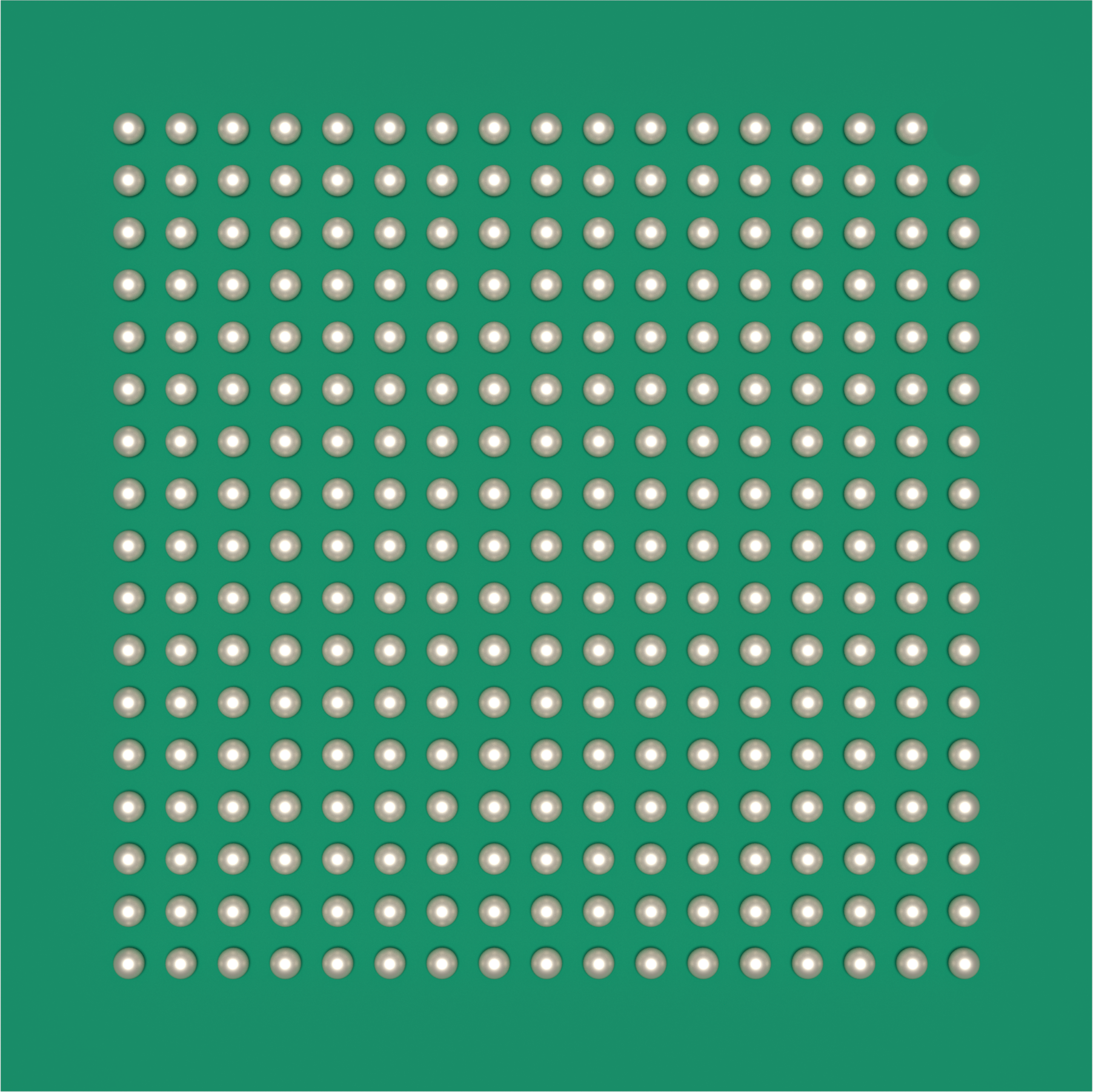

Тип корпуса

288-выводной пластмассовый корпус BGA288

Температурный диапазон

минус 40 – 85°С

.png)

cм

| CAN | 2 |

| fc [МГц] | 230 |

| I2C | 1 |

| tmax [С°] | 85 |

| tmin [С°] | -40 |

| Ucc_max [В] | 3,6 |

| Ucc_min [В] | 3,0 |

| Выводов | 288 |

Подписаться на обновления

Наши достижения

3 000 000 шт.

Микросхем в год

22 000 м2

Площадь помещений

1000 Партнеров по всему миру

290 Выполненных НИОКР

.png)

.png)